同步RAM与异步RAM

利用 $vivado$ 定制同步/异步 RAM 核并观察不同的行为特征。

1. 观察同步RAM行为状态

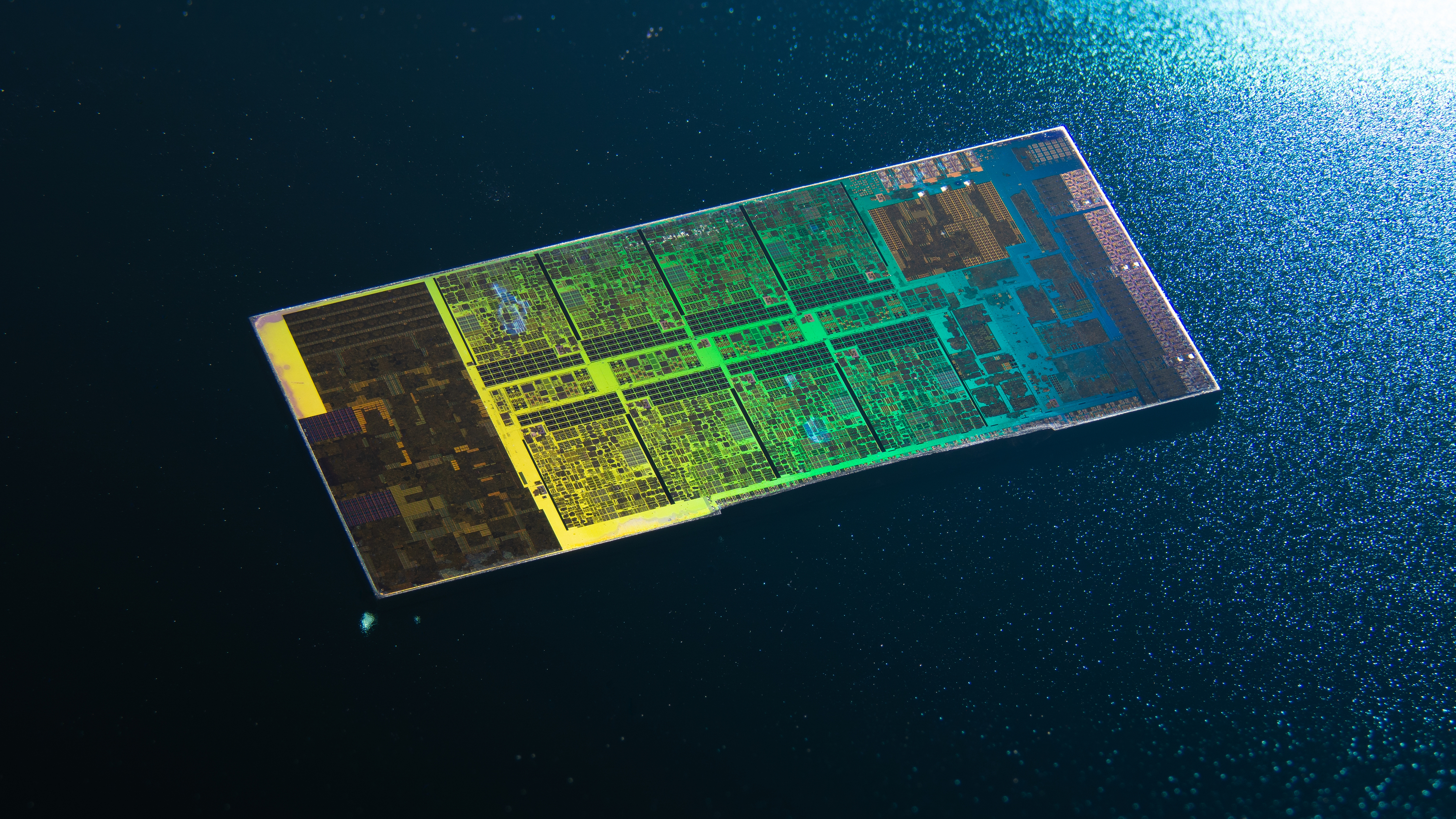

定制的IP核如下:

可见RAM有四个读入口和一个输出口,分别是:

$addr$ :地址

$clk$:时钟信号

$din$:写入数据

$dout$:读出数据

$we$:写使能信号

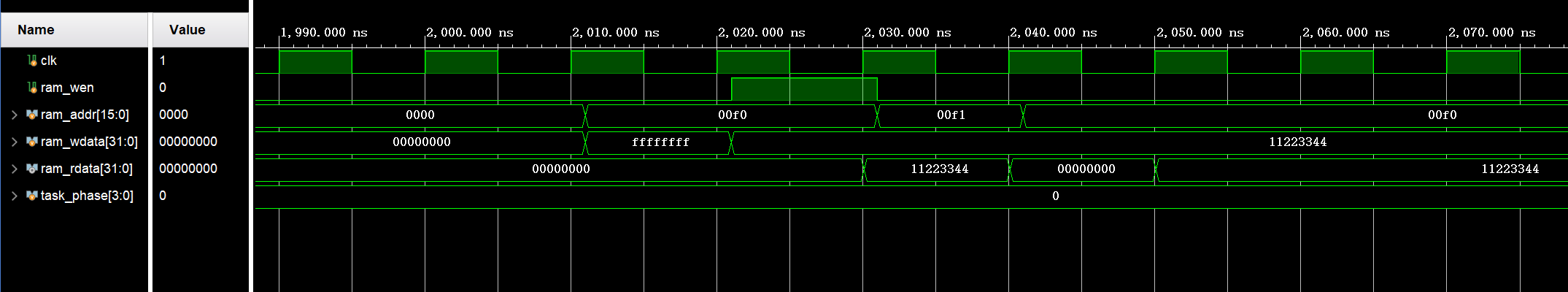

写入 $tb$ 文件后得到的波形如下:

可以看到,在时钟的上升沿 RAM 读出数据;当写使能有效时,只在时钟上升沿**读出地址 $addr$ 的数据。

2. 观察异步RAM行为状态

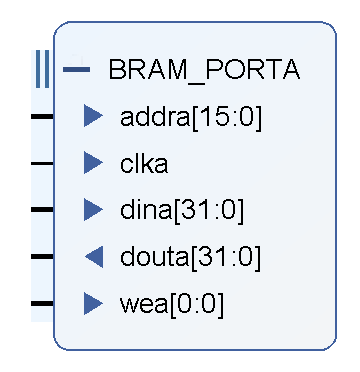

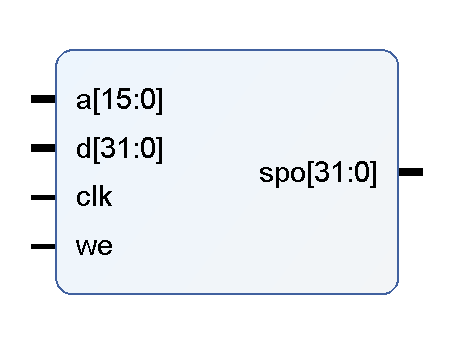

定制的IP核如下:

可见RAM有四个读入口和一个输出口,分别是:

$a$ :地址

$clk$:时钟信号

$d$:写入数据

$spo$:读出数据

$we$:写使能信号

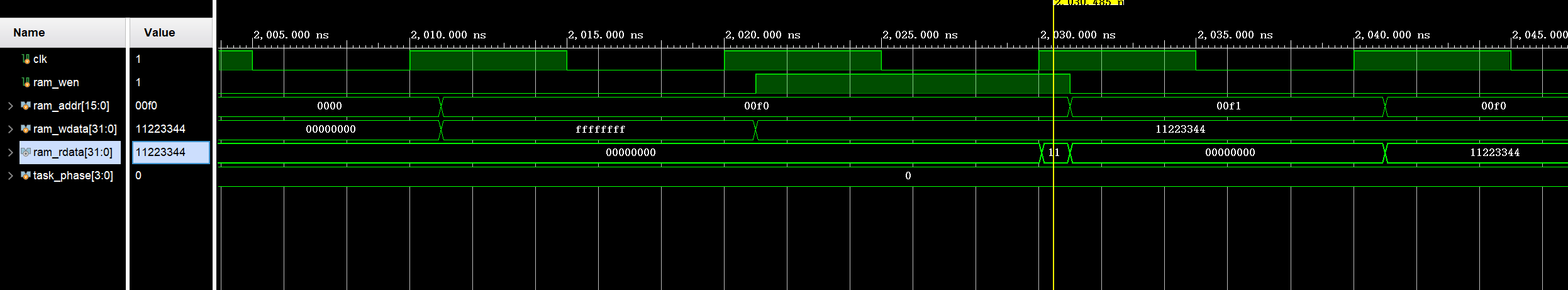

写入 $tb$ 文件后得到的波形如下:

可以看到,在时钟的上升沿 RAM 读出数据;当写使能有效时,立刻读出现在的地址 $addr$ 的数据。

本博客所有文章除特别声明外,均采用 CC BY-NC-SA 4.0 许可协议。转载请注明来自 Arn01d's planet!